# Adaptive Voltage Scaling (AVS)

Alex Vainberg Email: alex.vainberg@nsc.com October 13, 2010

**Design Implementation**

Hardware Performance Monitors Overview

### **AVS Introduction, Technology and Architecture**

**Design Implementation**

**Hardware Performance Monitors Overview**

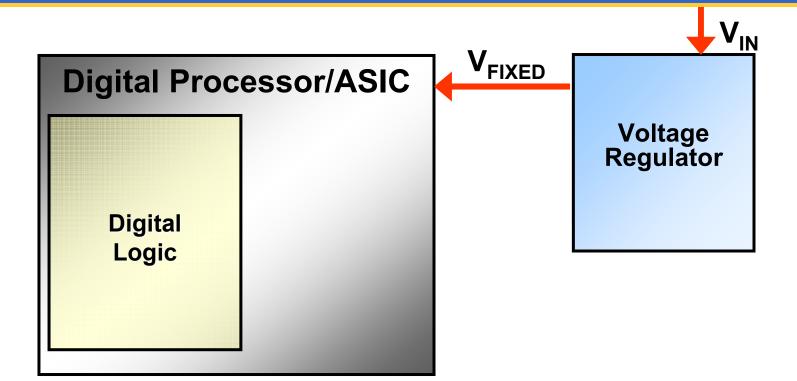

### **Traditional Power Management Delivery**

Fixed Voltage = Inefficient System!!!

- No temperature compensation

- No adjustment for lower voltages at lower frequencies

- No compensating for process variation

# **PowerWise® Adaptive Voltage Scaling (AVS)**

Adaptive Voltage Scaling = Maximum power savings

- Process and Temperature Compensation

- No need for frequency-voltage lookup tables

- Real-time continuous closed-up

PWI = PowerWise Interface

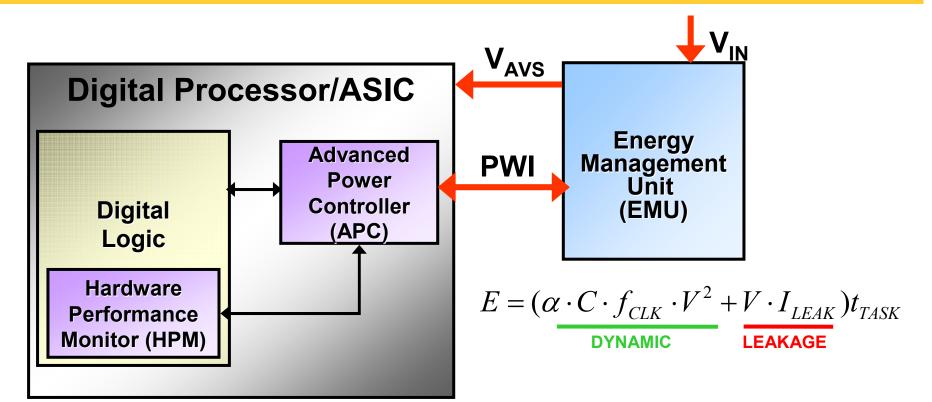

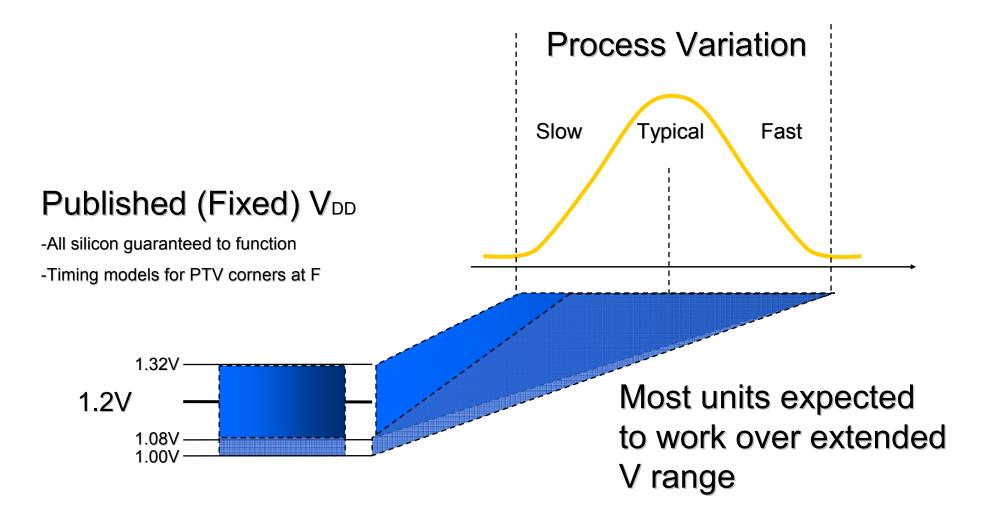

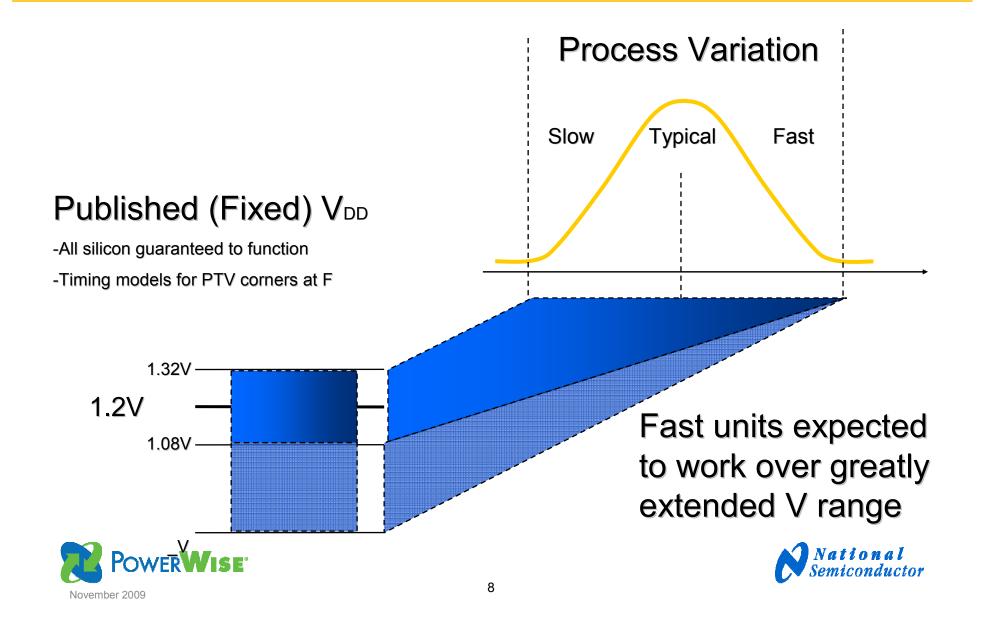

# **Operating Vdd Range – Device Performance Distribution**

### **Optimizing Power Efficiency**

### **Optimizing Power Efficiency**

### **AVS Optimizing Power / Full Range**

### Published (Fixed) VDD

- All silicon guaranteed to function

- Timing models for PTV corners at F

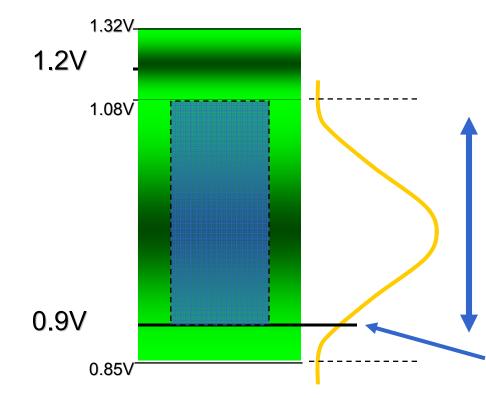

### AVS\_Vdd for Lowest Power

-Power controller maintains Vdd to lowest level possible based on on-chip PTV performance measurement

- Slow silicon possible lower Vdd based on slack timing

### Clamp Minimum VDD

- Independent clamp level for minimum Vdd set with power controller

- Overrides monitor request to go to a lower Vdd

### **Process Variability Comparison**

| NMOS    |                                                                  |                                                             |                                       |                                     |                                       |                            |                                  |                                                          |  |

|---------|------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|-------------------------------------|---------------------------------------|----------------------------|----------------------------------|----------------------------------------------------------|--|

|         | Performance Spread                                               |                                                             |                                       |                                     |                                       |                            |                                  |                                                          |  |

|         |                                                                  | Voltage                                                     |                                       |                                     | Temperature                           |                            | Voltage                          |                                                          |  |

|         | I <sub>Dsat</sub> [uA/um]                                        | V <sub>dd</sub> -10%                                        | 125°C                                 | 25°C                                |                                       |                            | -45°C                            | V <sub>dd</sub> +10%                                     |  |

|         | Corner                                                           | SS                                                          | SS                                    | SS                                  | Π                                     | FF                         | FF                               | FF                                                       |  |

|         | 0.13µm                                                           | -39.60%                                                     | -24.91%                               | -14.46%                             | 0.00%                                 | 14.19%                     | 25.05%                           | 46.17%                                                   |  |

|         | 90nm G                                                           | -42.73%                                                     | -28.55%                               | -20.04%                             | 0.00%                                 | 24.06%                     | 33.15%                           | 54.22%                                                   |  |

| SS      | 65nmG                                                            | -42.38%                                                     | -26.95%                               | -21.61%                             | 0.00%                                 | 23.32%                     | 30.55%                           | 55.01%                                                   |  |

| Process | 40nm G                                                           | -45.43%                                                     | -28.29%                               | -24.29%                             | 0.00%                                 | 23.76%                     | 30.61%                           | 52.34%                                                   |  |

| Pr      | 40nm LP                                                          | -47.87%                                                     | -29.36%                               | -25.30%                             | 0.00%                                 | 28.69%                     | 29.06%                           | 55.61%                                                   |  |

| PMOS    |                                                                  |                                                             |                                       |                                     |                                       |                            |                                  |                                                          |  |

|         |                                                                  | •                                                           |                                       | Perfo                               | Performance Spread                    |                            |                                  |                                                          |  |

|         | ,                                                                | Voltage                                                     |                                       |                                     | Temperature                           | Voltage                    |                                  |                                                          |  |

|         |                                                                  | vortage                                                     |                                       |                                     |                                       |                            |                                  |                                                          |  |

|         | I <sub>Dsat</sub> [uA/um]                                        | V <sub>dd</sub> -10%                                        | 125°C                                 |                                     | 25°C                                  |                            | -45°C                            | V <sub>dd</sub> +10%                                     |  |

|         |                                                                  |                                                             | 125°C<br>SS                           | SS                                  |                                       | Æ                          | -45°C<br>FF                      |                                                          |  |

|         | I <sub>Dsat</sub> [uA/um]                                        | V <sub>dd</sub> -10%                                        |                                       |                                     | 25°C                                  | <b>FF</b><br>13.84%        |                                  | V <sub>dd</sub> +10%                                     |  |

|         | I <sub>Dsat</sub> [uA/um]<br>Corner                              | V <sub>dd</sub> -10%<br>SS                                  | SS                                    | SS                                  | 25°C<br>TT                            |                            | Æ                                | V <sub>dd</sub> +10%<br>FF                               |  |

| SS      | I <sub>Dsat</sub> [uA/um]<br>Corner<br>0.13µm                    | V <sub>dd</sub> -10%<br>SS<br>-35.11%                       | SS<br>-16.67%                         | <b>SS</b><br>-13.96%                | 25°C<br>TT<br>0.00%                   | 13.84%                     | <b>₩</b><br>19.25%               | V <sub>dd</sub> +10%<br>FF<br>44.89%                     |  |

| ocess   | I <sub>Dsat</sub> [uA/um]<br>Corner<br>0.13µm<br>90nm G          | V <sub>dd</sub> -10%<br>SS<br>-35.11%<br>-37.46%            | SS<br>-16.67%<br>-20.87%              | <b>SS</b><br>-13.96%<br>-19.29%     | 25°C<br>TT<br>0.00%<br>0.00%          | 13.84%<br>24.03%           | <b>₩</b><br>19.25%<br>29.03%     | V <sub>dd</sub> +10%<br>FF<br>44.89%<br>54.90%           |  |

| Process | I <sub>Dsat</sub> [uA/um]<br>Corner<br>0.13µm<br>90nm G<br>65nmG | V <sub>dd</sub> -10%<br>SS<br>-35.11%<br>-37.46%<br>-39.73% | \$\$<br>-16.67%<br>-20.87%<br>-22.23% | SS<br>-13.96%<br>-19.29%<br>-20.30% | 25°C<br>TT<br>0.00%<br>0.00%<br>0.00% | 13.84%<br>24.03%<br>20.13% | FF<br>19.25%<br>29.03%<br>25.28% | V <sub>dd</sub> +10%<br>FF<br>44.89%<br>54.90%<br>52.65% |  |

### **Design Implementation**

**Hardware Performance Monitors Overview**

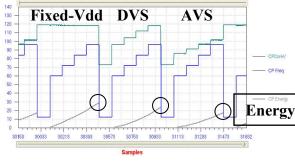

# **AVS Results on 130nm**

- ARM926EJ-S core

- Voltage and frequency scaling of CPU, Caches

- Four performance points:

- 60, 120, 180, 240 MHz

- 0.7V 1.2V Adaptive Voltage Range

- Dual ARM7 CPU cores

- Voltage and frequency scaling of ARM7

- Performance points:

- 96, 84, 72, 60, 12 MHz

- 0.7V 1.2V Adaptive Voltage Range

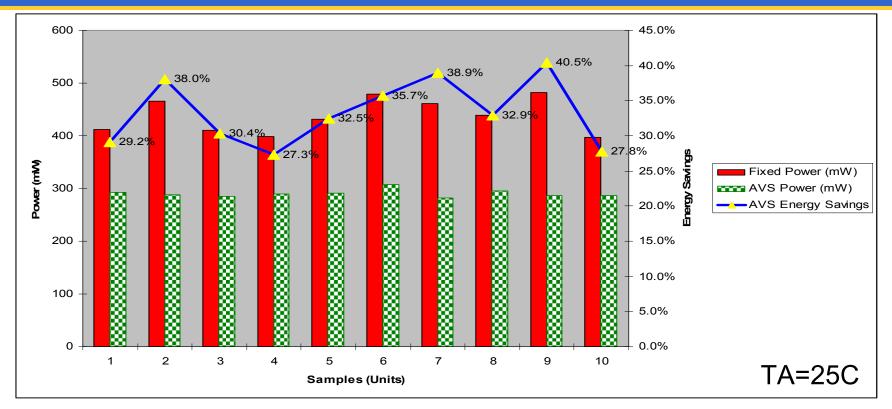

### **Measured AVS Power Savings**

- Custom ASIC/SoC design

- process 65nm, freq. greater than 750Mhz

- AVS reduced core power by 27 to 40% at maximum frequency

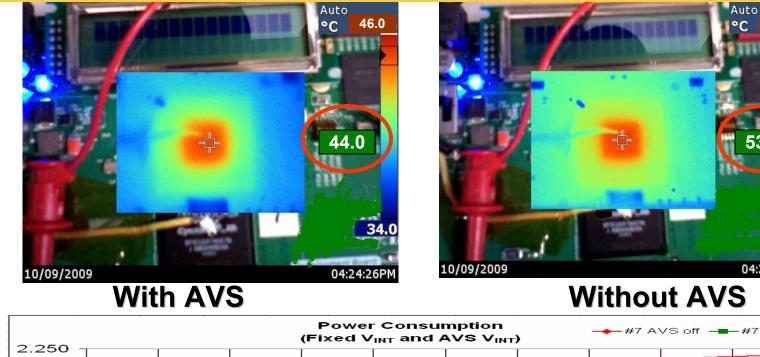

### **Power Saving and Thermal Performance, 65nm process**

56.0

27.0

04:28:35PM

........

November 2009

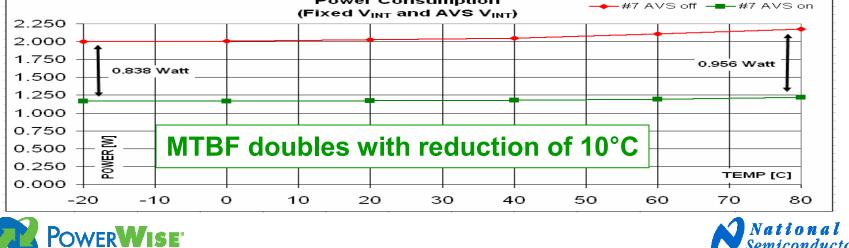

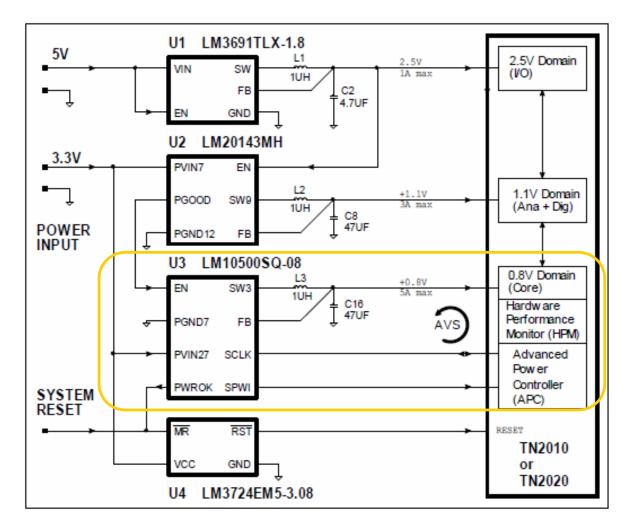

### **TN2020 & NSC power solution**

### **Measurements – TN20xx**

#### Board 29

#### Measured

Measured

| Тетр  | AVS OFF |              |       |         | AVS ON |              |       |         | Power<br>Savings |

|-------|---------|--------------|-------|---------|--------|--------------|-------|---------|------------------|

| deg C | mV      | mV (c. sns.) | А     | Power W | mV     | mV (c. sns.) | А     | Power W |                  |

| -20.3 | 805.78  | 11.92        | 1.679 | 1.353   | 727.7  | 10.7         | 1.506 | 1.096   | 19.0%            |

| 18.7  | 810.16  | 14.78        | 2.082 | 1.687   | 718.8  | 12.9         | 1.814 | 1.304   | 22.7%            |

| 58.2  | 813.88  | 19.36        | 2.727 | 2.219   | 709.6  | 16.3         | 2.298 | 1.630   | 26.5%            |

| 98.0  | 818.14  | 29.31        | 4.128 | 3.377   | 699.7  | 23.7         | 3.332 | 2.332   | 31.0%            |

#### Board 30

| Doard 30 |         |              |       |         |        |              |       |         | Weasureu         |

|----------|---------|--------------|-------|---------|--------|--------------|-------|---------|------------------|

| Тетр     | AVS OFF |              |       |         | AVS ON |              |       |         | Power<br>Savings |

| deg C    | mV      | mV (c. sns.) | А     | Power W | mV     | mV (c. sns.) | А     | Power W |                  |

| -20.3    | 805.6   | 11.51        | 1.621 | 1.306   | 722.3  | 10.3         | 1.451 | 1.048   | 19.8%            |

| 18.1     | 811.75  | 14.17        | 1.996 | 1.620   | 713.7  | 12.3         | 1.735 | 1.238   | 23.6%            |

| 58.2     | 817.64  | 18.39        | 2.590 | 2.118   | 704.3  | 15.5         | 2.176 | 1.533   | 27.6%            |

| 98.0     | 824.11  | 26.8         | 3.775 | 3.111   | 695.0  | 21.2         | 2.986 | 2.075   | 33.3%            |

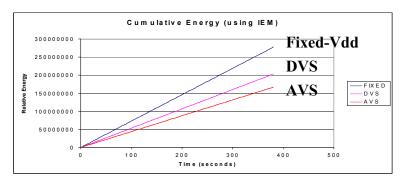

### **AVS System Impact**

### System Performance

- Once enabled AVS runs in background

- No processing overhead

### • Energy Savings – Scaled Voltage Domain

- Savings vary depending on process geometry, design implementation, and frequency scaling profile

- Expected energy savings for typical silicon will be 20-50% based on process and temperature variations

### System Risk Mitigation

- AVS is an additional function in the ASIC/Processor and the power conversion device

- AVS compliant ASIC/Processor and power conversion devices can still operate at fixed voltage or DVS without any design changes

**AVS Introduction, Technology and Architecture**

**Design Implementation**

### **Hardware Performance Monitors Overview**

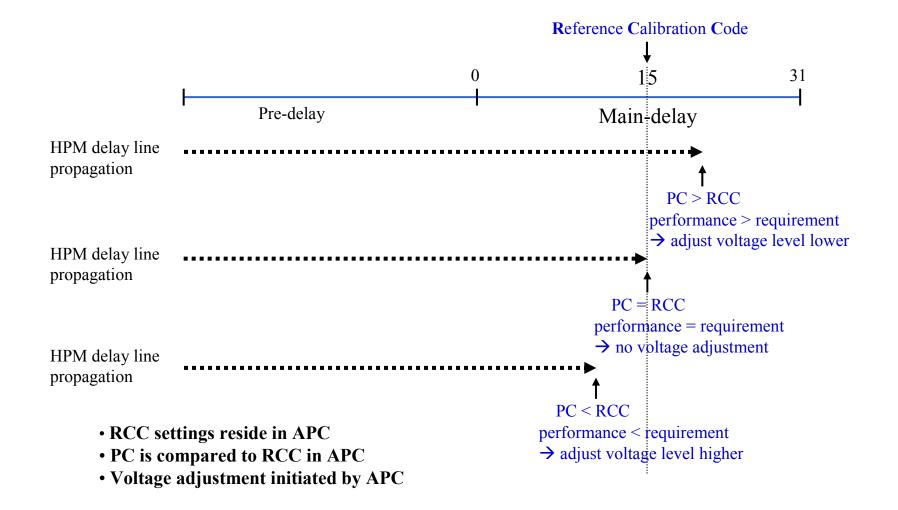

### **HPM Overview**

- HPM is Embedded in the voltage domain that is AVS controlled

- HPM translates the voltage level into silicon performance information

- HPM generated silicon performance information is a function of voltage level and HPM clock

- APC makes use of silicon performance information to determine the optimum voltage level for the required target performance

- Structurally coded synthesizable RTL to facilitate ease of layout P&R for optimizing silicon performance tracking accuracy

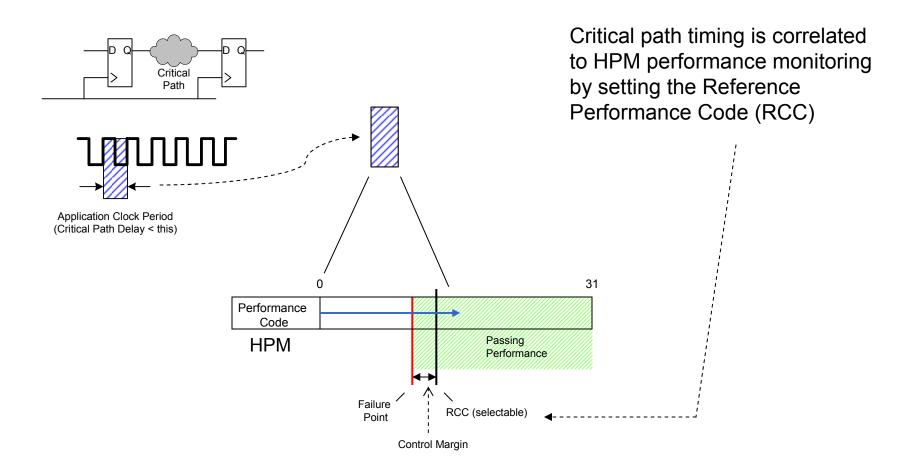

### **HPM and Critical Path Monitoring**

### HPM Performance Code and APC Voltage Control

**AVS Introduction, Technology and Architecture**

**Design Implementation**

**Hardware Performance Monitors Overview**

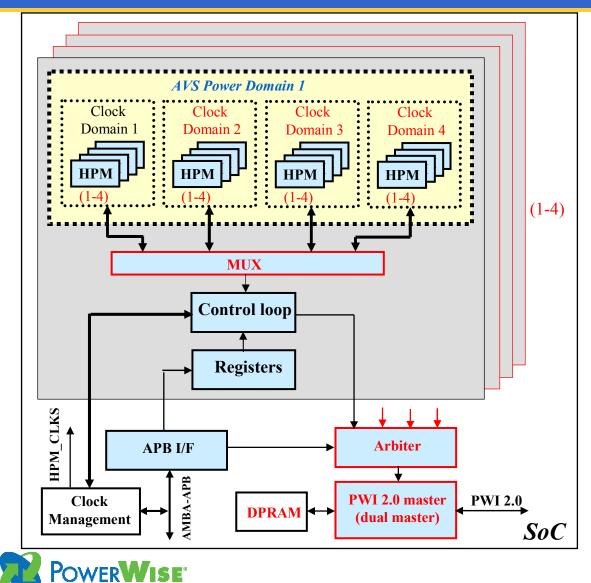

### **APC2 IP SoC View**

- Up to 4 AVS domains

- 1 4 per scalable clocks per AVS domain

- 1-4 HPM per clock domain

- APC2

- PWI2.0 interface master

- Up to 4 AVS domains

- Enhanced control-system

- Adaptive Voltage Scaling closed-loop control based on performance measurement data sampled by HPM

- Open-loop voltage scaling via voltage register table

- 8 performance levels + retention level

- Control registers programmed via AMBA-APB interface

- Auto PL0 back-bias

- Trace port for debug

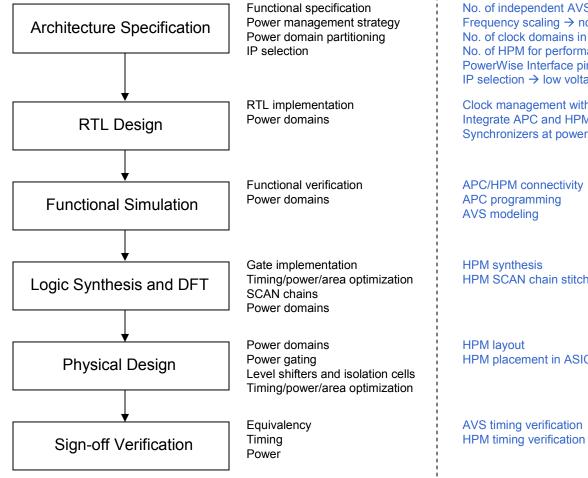

### **AVS Design Flow**

### **Power-aware ASIC Design Flow**

### Adding the AVS

|         | No. of independent AVS power domains<br>Frequency scaling → no. of performance levels<br>No. of clock domains in each AVS power domain<br>No. of HPM for performance tracking<br>PowerWise Interface pins<br>IP selection → low voltage std cells and memoriesAPC/HPM<br>Configurations |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Clock management with performance level interface<br>Integrate APC and HPMs<br>Synchronizers at power domain boundary                                                                                                                                                                   |

|         | APC/HPM connectivity<br>APC programming<br>AVS modeling                                                                                                                                                                                                                                 |

|         | HPM synthesis<br>HPM SCAN chain stitching                                                                                                                                                                                                                                               |

| 6  <br> | HPM layout<br>HPM placement in ASIC                                                                                                                                                                                                                                                     |

|         | AVS timing verification                                                                                                                                                                                                                                                                 |

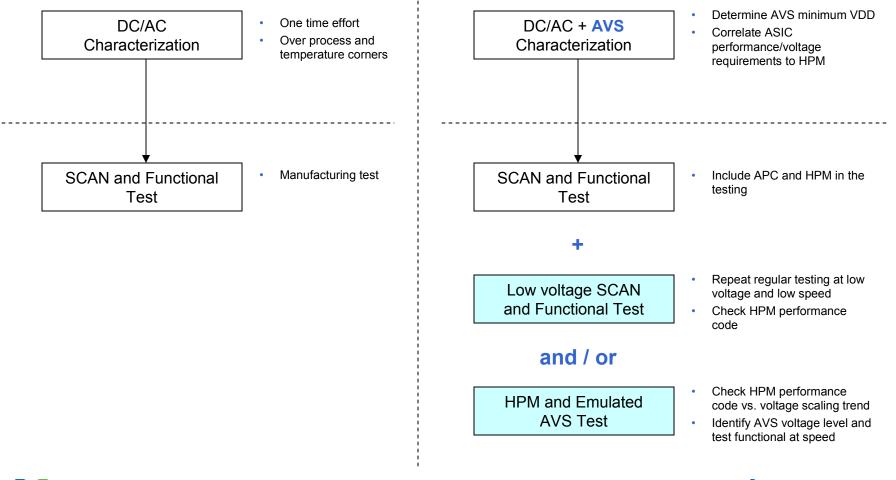

### **AVS Production Flow**

### **Typical ASIC Production Flow**

**AVS ASIC Production Flow**

N**ational** Semiconductor